RISC-V : Quintauris part à l’assaut du monde

Faut prendre des RISC dans la vie

Le 26 décembre 2023 à 16h08

5 min

Hardware

Hardware

En août, Bosch, Infineon Technologies, Nordic Semiconductor, NXP Semiconductors et Qualcomm Technologies s’associaient afin d’accélérer le développement de RISC-V. Nous savions simplement que l’alliance était basée en Allemagne.

Voilà Quintauris, avec Alexander Kocher à sa tête

Les cinq partenaires reviennent sur le devant de la scène avec un nom officiel pour leur alliance : Quintauris. « Toutes les approbations réglementaires requises ont été obtenues et Quintauris a été officiellement fondée le vendredi 22 décembre 2023 », précise le communiqué.

On apprend au passage qu’Alexander Kocher prend le poste de CEO. Il était auparavant chez Elektrobit, une société allemande (appartenant à 100 % à Continental AG) spécialisée dans le matériel et les logiciels embarqués et connectés pour l’automobile. Il l’a dirigée pendant cinq ans, jusqu’en décembre 2020.

Son profil LinkedIn ne précise pas ce qu’il a fait durant les trois dernières années. En mars 2022, Real-Time Innovations (RTI), spécialisée dans les voitures autonomes, annonçait néanmoins l’arrivée d’Alexander Kocher comme conseiller. D’après la liste des membres de RTI, il serait toujours présent au conseil consultatif. Dans tous les cas, il connait bien le monde de la voiture, première cible de Quintauris.

« Nous allons offrir à la prochaine génération de hardware des innovations et des possibilités d’évolution révolutionnaires, en mettant l’accent sur la combinaison des meilleurs éléments de RISC-V pour former une proposition unifiée et commercialisée », affirme le nouveau CEO. On n’est pas loin du dessin de xkcd sur les standards… De belles promesses, comme toujours lorsqu’une alliance se lance. Il faut maintenant convaincre des partenaires et le marché.

Automobile pour commencer, mobile et IoT à suivre

Il ne faut par contre pas compter sur le site mis en ligne pour avoir de plus amples détails. On y apprend tout de même que les efforts seront dans un premier temps « axés sur l'automobile », avec la possibilité d’y ajouter « le mobile et l'IoT ».

Quintauris se présente comme un élément central pour mettre « en œuvre de produits compatibles basés sur RISC-V, fournir des architectures de référence et aider à établir des normes industrielles ».

Comme c’était déjà le cas en août, les cinq partenaires lancent un appel aux « industriels, dirigeants et gouvernements [pour] soutenir cette initiative » et les rejoindre. Quintauris ne précise pas si d’autres participants sont venus se greffer au cours des quatre derniers mois. Seule certitude, aucun membre fondateur n’est venu s’ajouter.

Quintauris vs RISC-V Software Ecosystem vs OpenHW Group…

Dans la FAQ, on tourne un peu en boucle sur les points que nous venons de citer, jusqu’à une question intéressante : en quoi Quintauris est différente de RISC-V Software Ecosystem (RISE) ? Cet autre projet, soutenu par la Linux Foundation, s’est lancé en mars 2023 et s’oriente exclusivement, comme son nom l’indique, sur la partie logicielle. L'intérêt des nouvelles puces est en effet limité si le logiciel ne suit pas.

Le manifeste de RISE est d’ailleurs sans ambiguïté : « Permettre la commercialisation de logiciels pour les processeurs d'application utilisant l'architecture RISC-V pour des segments tels que la téléphonie mobile, l'électronique grand public, les centres de données et l'automobile ». RISE pour le logiciel, Quintauris pour le matériel.

Fin novembre, Canonical a rejoint RISE. Le père d’Ubuntu rejoint des géants du secteur comme Google, Intel, MediaTek, Qualcomm, NVIDIA, Red Hat, Samsung, SiFive, AMD, Microchip… Rien de bien étonnant puisque, en octobre, Ubuntu 23.10 était mis en ligne avec le support de la puce SiFive HiFive Pro P550 et affirmait alors « être un fervent partisan de l’écosystème RISC-V ».

Il existe d’autres organisations cherchant à promouvoir l’architecture RISC-V, OpenHW Group par exemple. En novembre, le groupe profitait du RISC-V Summit pour annoncer sa plateforme open-source CORE-V CVA6.

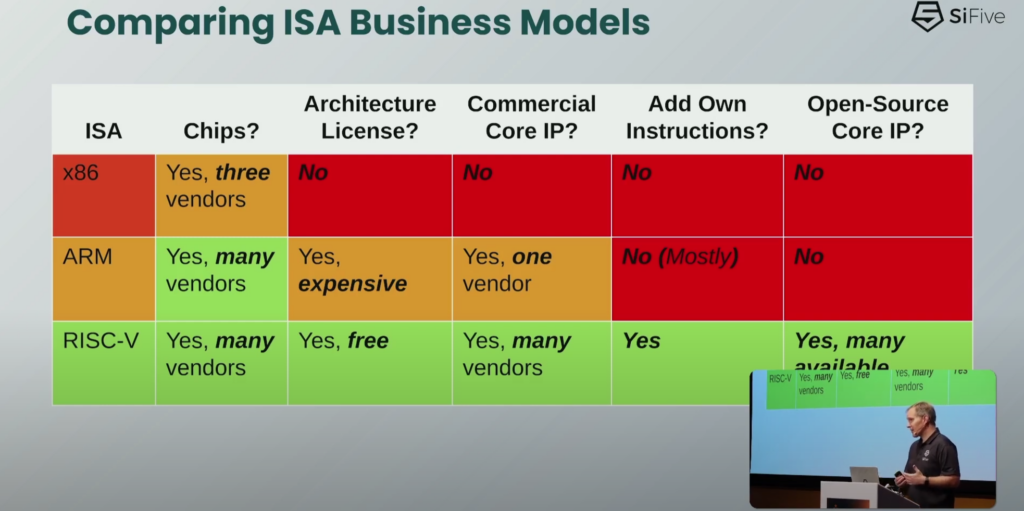

RISC-V vs ARM vs x86

Pour rappel, RISC-V est une architecture de jeu d'instructions ouverte et libre, disponible en version 32 à 128 bits. Chacun peut y ajouter ses propres instructions et elle prend en charge un très grand nombre de cœurs. C’est un sérieux concurrent aux solutions d’Arm.

Le mois dernier, lors de l'Ubuntu Summit 2023, John Ronco proposait une présentation de la « révolution RISC-V ». Il est chez SiFive depuis maintenant un an et membre du conseil d’administration de RISC-V Software Ecosystem (RISE). Il connait bien le sujet puisqu’il a été pendant huit ans chez ARM, notamment en tant que vice-président de différentes branches.

RISC-V : Quintauris part à l’assaut du monde

-

Voilà Quintauris, avec Alexander Kocher à sa tête

-

Automobile pour commencer, mobile et IoT à suivre

-

Quintauris vs RISC-V Software Ecosystem vs OpenHW Group…

-

RISC-V vs ARM vs x86

Commentaires (11)

Vous devez être abonné pour pouvoir commenter.

Déjà abonné ? Se connecter

Abonnez-vousLe 26/12/2023 à 20h44

Le 27/12/2023 à 10h50

Le 28/12/2023 à 13h13

C’est assez expérimental, assez lent pour le moment.

Rien que les maj sont compliquées ( j’ai eu un des premiers lots sur kickstarter) je pense qu’il’faudra encore quelques évolutions hardwares.

Mais je suis optimiste, arm a mis 15 ans avant de défier le x86 en perfs, la il y a du monde qui pousse derrière.

Le 28/12/2023 à 13h51

je vais suivre ça de près =)

Le 28/12/2023 à 16h54

L'un est un RISC-V 64GC (multiplication, division, atomicité, virgule flottante simple et double) et l'autre un 64GCV (donc avec des instructions vectorielles en plus).

Les deux sont assez chères, mais se battent en perfs quelque part entre les RPI 4 et 5 (plus proches du 4).

Fonctionnellement, on y est pas encore, les fonctionnalités avancées dans les datasheets niveau multimédia sont encore à venir niveau soft mais ça avance.

Les fonctionnalités de virtualisation/protection sont encore en évolution.

Le 26/12/2023 à 23h13

Le 27/12/2023 à 10h20

Je trouve effectivement que c'est du grand n'importe quoi.

Le 27/12/2023 à 10h46

RISC-V est découpé en tranches pour plus d'adaptabilité: instructions entières, multiplication/division, instructions compressées, virgule flottante, protection mémoire ... toute est "à la carte".

Quand aux implémentations, elles sont à la carte aussi: avec/sans cache, câblé ou en pipeline, in order ou out-of-order... Là on touche à des perfs entre x1 et x3 pour les mêmes instructions.

RISC-V n'est pas le messie attendu dans les CPU, c'est le messaie dans les micro-contrôleurs et l'embarqué. Pour le moment, aucune implémentation ne se mesure à des ARM sortis il y a 5 ans. Et dans le même temps, ARM contre-attaque en faisant des archi pour micro contrôleurs 2x plus performantes que leurs anciennes...

Actuellement, les cartes RISC-V peinent à atteindre les perfs des RPI 1 et 2!

Le 26/12/2023 à 23h18

Ils ont connecté les pinuches du chip n'importe comment, je suis sûr que c'est encore Flock qui a voulu faire de l'art au lieu du DRC

---> []

Le 27/12/2023 à 09h42

Ca ressemble plutôt à une photo d'un processeur.

Le 27/12/2023 à 21h21

Merci FrancoisA, mais ce n'est pas une photo et je trouve que ça illustre très mal un CPU sur un PCB :

Le 1er truc qui me hérissait le poil c'est que les pistes de cuivres sont dans un pitch qui n'a rien à voir avec les pinuches des 7 packages autour.

Du coup en regardant un peu plus, je constate aussi que les 4 capas rondes 16V devant sont nommées R30, R32, R35 et R35 encore ! Pareil pour les 3 quartz : RTC27 RTC27 again et RTC32.

On va passer les carrés 1R2, souvent du bobinage, commé Cxxx sur le PCB.

On dirait une vision art abstrait de l'électronique. Ou alors ils ont tout fait pour obfusquer le PCB et empécher le reverse-engineering ?