Microsoft détaille les caractéristiques de sa puce Maia 100 pour l’IA

Si tu empêches Maia de butiner les données, tu n'auras pas d’IA

En novembre de l’année dernière, Microsoft annonçait deux puces développées maison : le CPU Cobalt 100 et « l’accélérateur » Maia 100 pour l’intelligence artificielle. Assez peu de détails étaient donnés : 105 milliards de transistors et gravure en 5 nm. La société a profité du Hot Chips 2024 pour dévoiler davantage de précision.

Le 30 août à 16h19

4 min

Hardware

Hardware

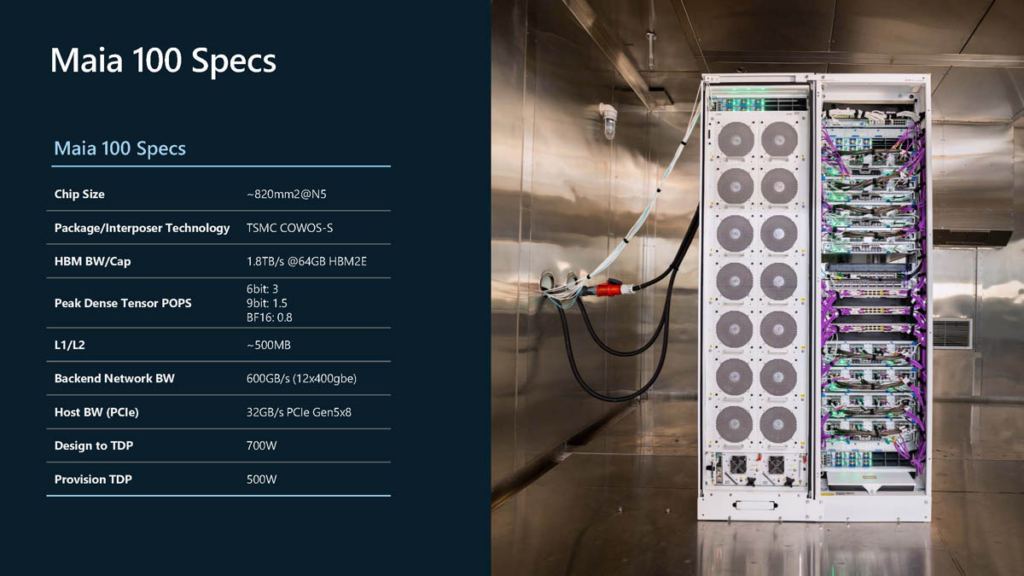

Cette puce occupe 820 mm² et exploite donc le processus de gravure N5 de TSMC, avec la technologie CoWoS-S (Chip-on-Wafer-on-Substrate) de TSMC. Au niveau superficie du SoC, c’est assez proche des puces H100 de NVIDIA (814 mm²) et A100 (826 mm²).

Microsoft reste sur la HBM2E

Maia 100 intègre 105 milliards de transistors, contre 80 milliards pour H100 et 54 milliards pour A100. Blackwell fait plus que doubler la mise, mais avec une architecture double. On y retrouve 208 milliards de transistors, enfin 2x 104 milliards serait plus exact. La superficie de la puce B200 n’est pas (encore) précisée.

Maia 100 intègre 64 Go de HBM2E (sous la forme 4x 16 Go) à 1,8 To/s. NVIDIA et AMD sont pour rappel passés sur la HBM3 pour leurs dernières puces haut de gamme, tandis que Microsoft prend donc le pari de rester sur la génération précédente. Si les performances sont moindres, la disponibilité pourrait être moins problématique qu’en HBM3.

Toujours sur la mémoire, Microsoft ajoute environ 500 Mo de cache L1 et L2 combinés, sans donner la répartition.

4 tuiles par cluster, 16 cluster par SoC

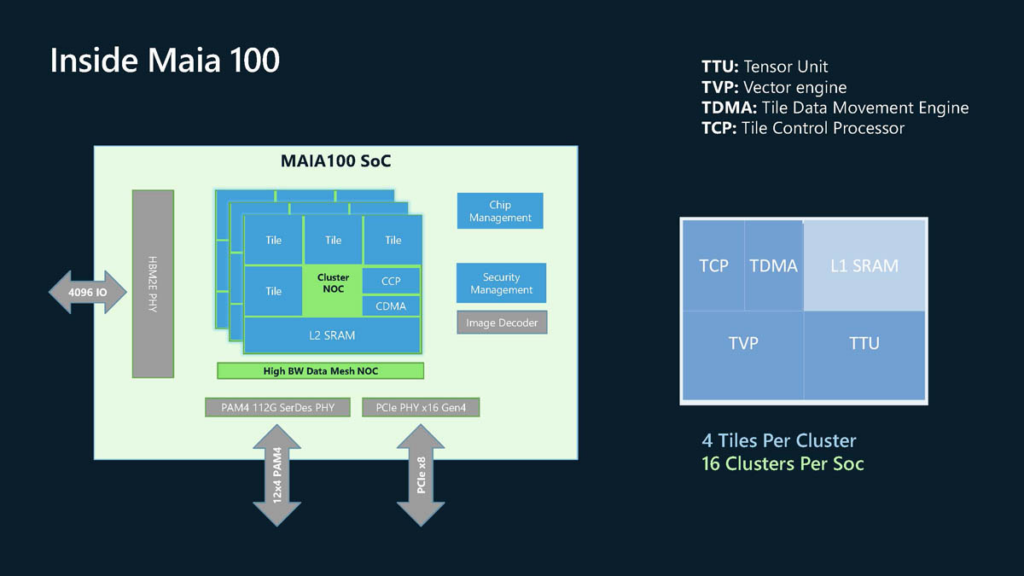

Lors d’une présentation reprise par ServTheHome, Microsoft a partagé plus d’informations sur la conception interne des puces. On apprend dans l’image ci-dessous notamment qu’il y a quatre tuiles – TTU (Tensor), TVP (Vector), TDMA (Data movement) et TCP (Control processor) – par cluster et 16 clusters par SoC.

6/9 bits, BF16 et TDP

La puce Maia 100 prendra en charge les nombres sur 6 bits, 9 bits, en BF16 et FP32. Microsoft ne donne pas tous les détails pour l’instant.

NVIDIA est descendu en 8 bits (FP8) avec Hopper et jusqu’à 4 et 6 bits (FP4/FP6) avec Blackwell qui devrait arriver d’ici à la fin de l’année. Deux experts de l’intelligence artificielle nous avaient détaillé l’intérêt de cette baisse de la précision, sur la rapidité notamment. Et si ces termes ne vous parlent pas, on a aussi un dossier sur les nombres en informatique !

La puce peut supporter un TDP de 700 watts, mais ne devrait utiliser que 500 watts.

Microsoft ne semble pas venir jouer sur les platebandes des Instinct MI300x et autres Blackwell de NVIDIA au niveau de la performance pure, mais davantage sur un bon ratio entre performances et consommation. À voir…

Ultra Ethernet et RoCE

Le réseau peut monter jusqu’à 12x 400 GbE, soit un total de 600 Go/s. Sur la partie réseau toujours, Microsoft rappelle son implication dans l’Ultra Ethernet Consortium qui développe l’Ultra Ethernet, pensé pour le HPC (calcul haute performance) et l’IA. Nous en avions discuté avec Rémy Gauguey, data center software architect chez le français Kalray et ancien du CEA. Microsoft ne s’étend par contre pas davantage sur l’Ultra Ethernet et son implication dans la conception de Maia 100.

L’entreprise explique simplement que l’interconnexion de sa puce « utilise un protocole personnalisé de type RoCE, offrant une fiabilité et un équilibre améliorés ». RoCE signifie RDMA over Converged Ethernet, tandis que RDMA (Remote Direct Memory Access) est issu du monde Infiniband et permet un accès direct à la mémoire.

On a évidemment les habituelles promesses d’un fabricant en pareille situation : « Avec une architecture matérielle et logicielle conçue dès le départ pour exécuter plus efficacement de grosses charges de travail, Maia 100 intègre ce que nous avons appris à travers chaque couche de notre architecture cloud ».

Un mot pour les devs

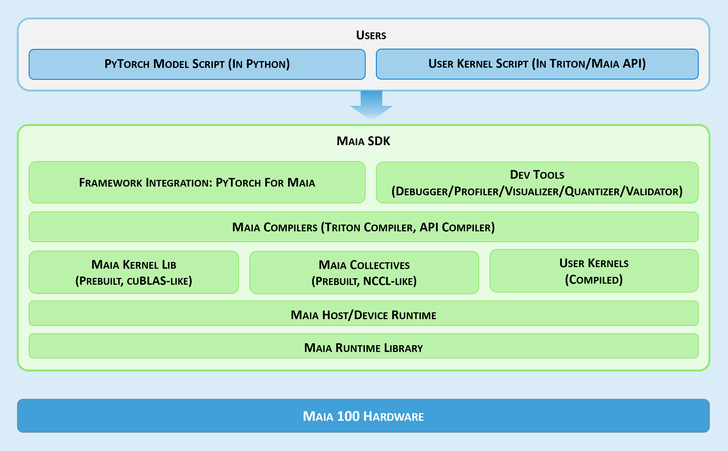

Pour les développeurs, un kit de développement (SDK) « permet aux utilisateurs de porter rapidement leurs programmes PyTorch et Triton vers Maia ». À ce stade, Microsoft ne précise en revanche pas plus avant le calendrier de déploiement de Maia 100.

Microsoft détaille les caractéristiques de sa puce Maia 100 pour l’IA

-

Microsoft reste sur la HBM2E

-

4 tuiles par cluster, 16 cluster par SoC

-

6/9 bits, BF16 et TDP

-

Ultra Ethernet et RoCE

-

Un mot pour les devs

Commentaires (4)

Vous devez être abonné pour pouvoir commenter.

Déjà abonné ? Se connecter

Abonnez-vousLe 31/08/2024 à 01h48

Le 31/08/2024 à 10h08

Vrai présage, nom stupide (pour une puce) ou fiction marketing, que la concurrence (de NVIDIA, entre autres) va gentiment écrabouiller façon Godzilla ?

Le 02/09/2024 à 08h37

Maia, un second couteau (aztèque) ?

Le 03/09/2024 à 08h48

C'est peut être aussi pour ça que MS c'est "contenté" de la HM2E, parce que c'est la seule disponible à date, vu qu'ils ont un poil trainé pour passer commande.