3D V-Cache : AMD dévoile sa solution pour des performances CPU encore meilleures dans les jeux

Paré pour Zen 4 ?

Notre dossier sur AMD au Computex 2021 :

Le 01 juin 2021 à 03h00

3 min

Hardware

Hardware

Vous pensiez que le cache L3 intégré aux processeurs Zen 3 était imposant ? Attendez de découvrir ce que permet le 3D V-Cache, qui consiste à en ajouter par-dessus le die d'une puce. De quoi gagner de la place pour les éléments dédiés au calcul et maximiser les performances. À quel prix ?

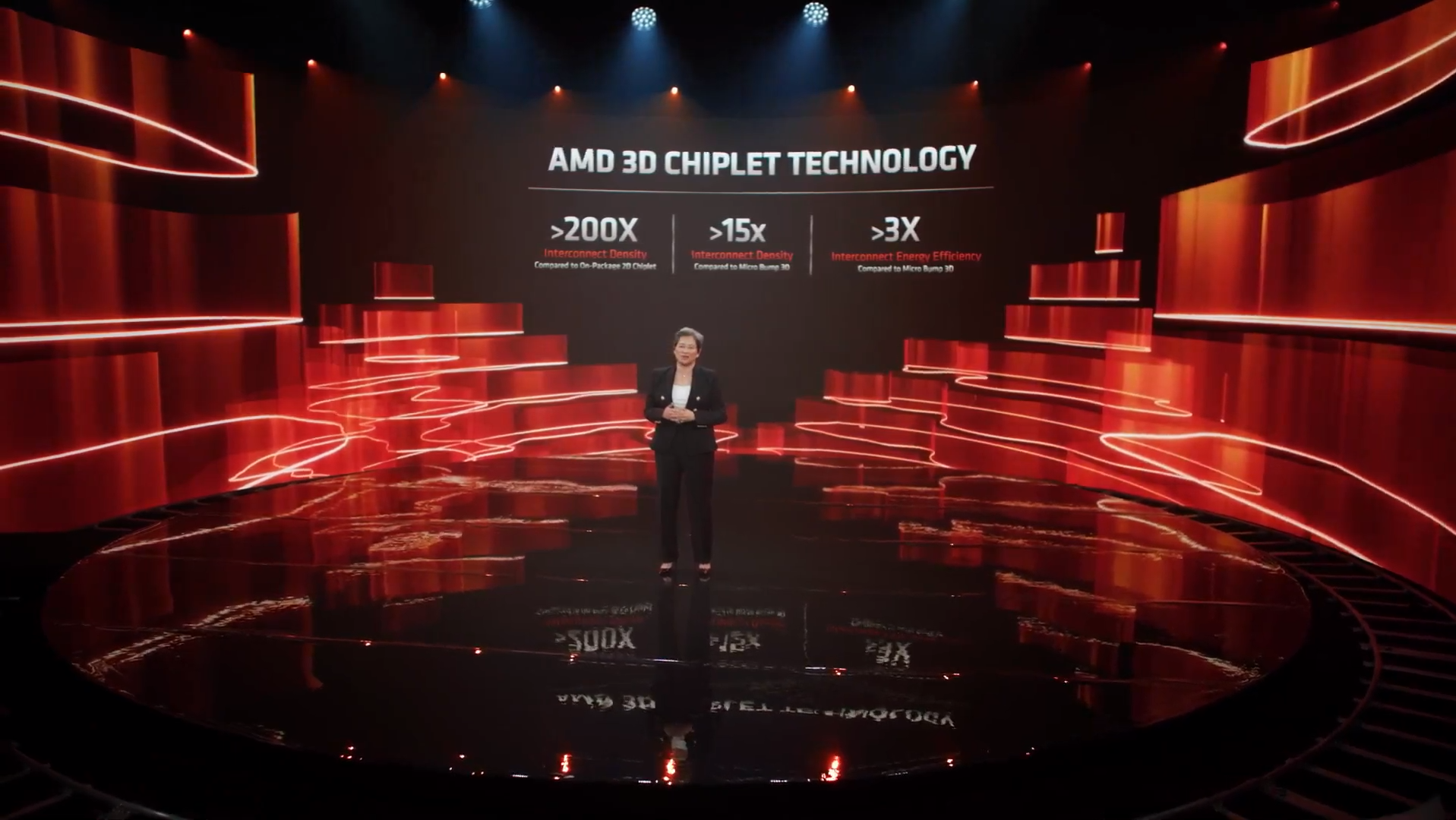

« Chez AMD, on n'a pas de CPU à plus de 5 GHz, mais on a des idées ». Voici en substance le message adressé par Lisa Su à la fin de sa conférence du Computex 2021. Elle a en effet évoqué la prochaine solution de packaging actuellement développée par la société et qui devrait être mis en production « d'ici la fin de l'année ».

- Ryzen 5000G(E) : AMD annonce des APU Zen 3 pour le 5 août, dès 259 dollars

- AMD Fidelity FX Super Resolution pour le 22 juin : les GeForce compatibles, peu de jeux concernés

- AMD lance ses Radeon RX 6000M (Navi 22/23) et sa plateforme AMD Advantage

- 3D V-Cache : AMD dévoile sa solution pour des performances CPU encore meilleures dans les jeux

Du cache par-dessus le die du CPU

On ne sait pas encore au sein de quel produit, mais une démonstration a été faite sur la génération actuelle de processeurs Ryzen, avec 64 Mo de cache L3 intégrés via un die spécifique, superposé sur celui du CPU (stacking 3D). Un bus d'interconnexion dédié est utilisé pour la communication (Through Silicon Vias, TSVs).

Son débit n'a pas été précisé, mais AMD dit que cette solution est la plus efficace dont elle dispose à date en termes de densité et d'efficacité énergétique. Lisa Su a précisé que l'apparence physique finale d'un die, et donc du processeur, est identique. Les performances dans les jeux d'un 5900X seraient, elles, bien plus élevées.

Elles seraient ainsi multipliées par 1,04x dans le pire des cas, 1,25x dans le meilleur, avec une moyenne à+ 15 %. Les conditions techniques n'ont néanmoins pas été précisées : GPU, définition, niveau de qualité graphique, etc.

Du cache, toujours plus de cache

Cette solution s'inscrit dans un mouvement assez large chez AMD qui consiste à miser sur l'intégration de caches de plus en plus large au sein de ses architectures afin de booster les performances. Cela a notamment été le cas de Zen au fil de son évolution, surtout avec Zen 3. RDNA 2 doit également beaucoup à son Infinity Cache.

Ce 3D V-Cache pourrait être l'une des armes utilisées par la société pour donner un coup de fouet à ses prochaines puces sans avoir à aller chercher des évolutions lourdes au niveau de l'architecture et son IPC. Cela peut aussi lui permettre d'avoir plus de cœurs au sein d'une même surface, le cache L3 étant alors superposé.

Reste une question qui n'a pas été évoquée par AMD : le coût d'une telle solution et son impact sur le prix final des produits. On attend également de voir si cela aura un intérêt pour des applications professionnelles où la puissance de calcul du CPU prime avant tout. Et là, un cache plus élevé ne pourra pas toujours sauver la mise.

3D V-Cache : AMD dévoile sa solution pour des performances CPU encore meilleures dans les jeux

-

Du cache par-dessus le die du CPU

-

Du cache, toujours plus de cache

Commentaires (18)

Vous devez être abonné pour pouvoir commenter.

Déjà abonné ? Se connecter

Abonnez-vousLe 01/06/2021 à 05h13

Il joue a cache cache ?!

Le 01/06/2021 à 06h40

Pourquoi le cache sur la puce que tient Lisa Su est sur un seul chiplet et pas les deux ?

Le 01/06/2021 à 07h06

Le 01/06/2021 à 07h10

Il y a un chiplet où il est exposé (pour montrer le résultat) et pas l’autre (pour montrer que physiquement rien ne change).

Non, on applaudit pas ce genre de choses !

Le 01/06/2021 à 07h25

Comment ce passe l’évacuation de la chaleur du cpu ? Elle traverse le cache, non ?

Le 01/06/2021 à 07h28

Rien avoir avec le stepping de zen 3 ?

Le 01/06/2021 à 07h30

Le 01/06/2021 à 07h52

Non pas tant que ça, le silicium est déjà un très bon conducteur thermique.

Le 01/06/2021 à 08h18

Rien. Voir ici.

Le 01/06/2021 à 08h19

De toutes façons si l’objectif c’est de réduire la densité 2D par la 3D, tu auras un même TDP sur moins de surface, donc mécaniquement… C’est pas pour rien qu’Intel a commencé avec Lakefield sur sa technologie de stacking 3D

C’est pas pour rien qu’Intel a commencé avec Lakefield sur sa technologie de stacking 3D

Le 01/06/2021 à 08h35

Pourquoi ne pas faire l’inverse, mettre le cache d’abord et le CCD au-dessus ?

Le 01/06/2021 à 08h36

Aucune idée ils n’ont pas détaillé. Mais s’ils le font, ils doivent sans doute avoir une raison ;) (sans doute pour faciliter les interconnexion du cache sur le CPU plutôt que l’inverse)

Le 01/06/2021 à 09h46

Je suppose bêtement que c’est pour les connexions aux PINs du socket (et/ou autres interconnexions).

C’est pareil pour la RAM des SoC, quand c’est stacké, c’est par le dessus en général.

Le 01/06/2021 à 10h16

Disons que in fine c’est le CPU qui sera à relier au socket, donc ça parait logique qu’il soit en bas. Mais n’ayant pas tous les détails, difficile d’en juger

Le 01/06/2021 à 15h55

Oui effectivement ça parait plus simple de mettre le CPU en bas

Le 02/06/2021 à 07h19

bonjour,

je suppose aussi que cela doit être la principale raison , puis le cache qui serait traversé par les pins ça semble pas top comme solution…

Le 02/06/2021 à 08h05

La techno qu’utilise AMD est la TSMC SoIC et TSMC indiquent qu’ils peuvent empiler jusqu’à 12 puces de mémoire les unes sur les autres, pour l’instant AMD se contente d’une seule puce mémoire empilée.

Le 02/06/2021 à 08h11

Oui, parce qu’ils empilent sur un CPU, avec un petit détail à prendre en compte : le TDP et le besoin de le dissiper