Les annonces autour des FPGA se multiplient, AMD présente Spartan UltraScale+

This is Spartan !

Alors qu’AMD annonce de nouveaux FPGA Spartan UltraScale+ qui arriveront l’année prochaine, nous en profitons pour faire un premier tout d’horizon des FPGA (sur lesquels AMD et Intel se sont jetés à coup de milliards de dollars) et de leur principe de fonctionnement. Si le cœur vous en dit, nous irons plus loin.

Le 05 mars à 15h36

6 min

Hardware

Hardware

Petit rappel utile sur la définition d’un FPGA : c’est un Field Programmable Gate Array (ou réseau de portes programmables in situ dans la langue de Molière). Le mot important dans le cas présent est « programmable ».

Pour rappel, dans une précédente actualité, nous avions déjà évoqué le cas des CPU, des SoC (System-on-chip, que l’on pourrait presque qualifier de processeurs tout-en-un) et des micro-contrôleurs.

Dis, c’est quoi un FPGA ?

Le FPGA est donc un circuit logique (re)programmable contrairement aux CPU et autres SoC. « Il s’agit de circuits composés de cellules qui, contrairement au CPU, peuvent être reprogrammées après fabrication. Les utilisateurs peuvent donc attribuer différentes fonctions aux cellules et redéfinir les interconnexions », explique Dell.

Un FPGA peut ainsi s’adapter très finement à un usage, et de ce fait proposer une grande efficacité énergétique : « Là où un CPU devra exécuter plusieurs milliers d’instructions, un FPGA pourra exécuter la même fonction en seulement quelques cycles et donc consommer moins d’énergie ».

Les FPGA ne sont pas nouveaux même s’ils ont le vent en poupe ces derniers temps. Ils se développent depuis une trentaine d’années, au moins, et les géants que sont AMD et Intel se sont jeté dessus depuis longtemps. L’École normale Supérieure de Lyon vantait, par exemple, ses mérites il y a déjà 20 ans.

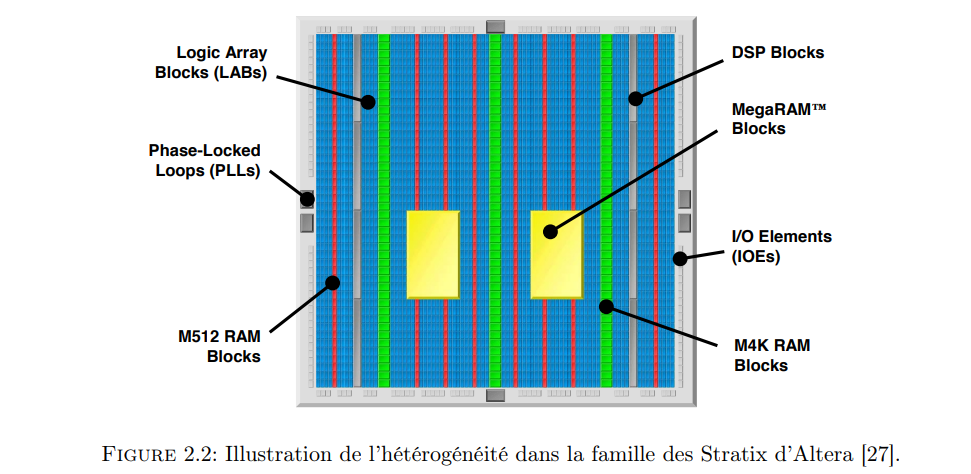

[caption id="attachment_130110" align="aligncenter" width="971"] Université de Louvain[/caption]

Université de Louvain[/caption]

Une « matrice de blocs de logique »

Nous ne rentrerons pas dans les détails techniques aujourd’hui, mais aborderons les grandes lignes. Les FPGA sont généralement structurés en îlot : « Il s’agit d’une matrice de blocs de logique liés par des canaux de routage. Cette matrice est entourée d’un anneau de contact (I/O) », explique l’université de Louvain.

Sébastien Peychet, de l’institut National des Sciences Appliquées de Lyon, ajoute qu’un FPGA peut être assimilé à « un circuit logique programmable, ou configurable, contenant quelques milliers à quelques dizaines de milliers de blocs logiques ». « Chaque bloc logique peut contenir une fonction combinatoire de quelques entrées (4 à 8) et de 1 à 4 bascules D, selon les générations », précise-t-il.

Un peu plus dans le détail, chaque bloc – on parle de CLB (Configurable Logic Block) chez AMD/Xilinx et de LAB (Logic Array Block) chez Intel/Altera – est découpé en tranches (slices), qui contiennent des cellules logiques.

Dans le monde des FPGA, on parle de « LUT » pour une table de correspondance (ou LookUp Table). Elle sert à implémenter des équations logiques avec des entrées et une sortie. « C’est de loin le circuit le plus polyvalent pour créer une fonction logique configurable », explique l’Université Numérique.

Altera et Xilinx : deux géants du FPGA rachetés par Intel et AMD

Les cas d’usage sont très nombreux puisque la puce s’adapte aux besoins, comme en témoignent les listes d’application chez AMD et chez Intel. AMD profite de son annonce du jour pour rappeler que des FPGA Spartan se trouvent dans « des rovers envoyés sur Mars » et des « défibrillateurs automatisés ».

Les deux spécialistes du CPU ne se sont pas lancés à partir d’une feuille vierge dans le monde des FPGA, ils ont ouvert en grand leur portefeuille. Le Texan a, en effet, pour rappel racheté Xilinx en 2020, un spécialiste dans ce domaine, pour la bagatelle de 35 milliards de dollars.

De son côté, Intel s’y était pris bien plut tôt en mettant dans sa besace Altera en 2015 pour 16,7 milliards de dollars. Preuve, s’il en était besoin, que c’est un domaine d’avenir pour les deux entreprises.

Ajoutons à cela qu’Intel vient de lancer une « nouvelle » filiale dédiée aux FPGA… Altera. Avec cette annonce, il s’agit donc simplement de donner de l’indépendance et de la visibilité à sa société spécialisée dans les circuits programmables. Elle propose des puces dans les gammes Agilex 3, 5, 7 et 9 (toute ressemblance avec la gamme des Core n’est pas fortuite).

Voici les FPGA Spartan UltraScale+

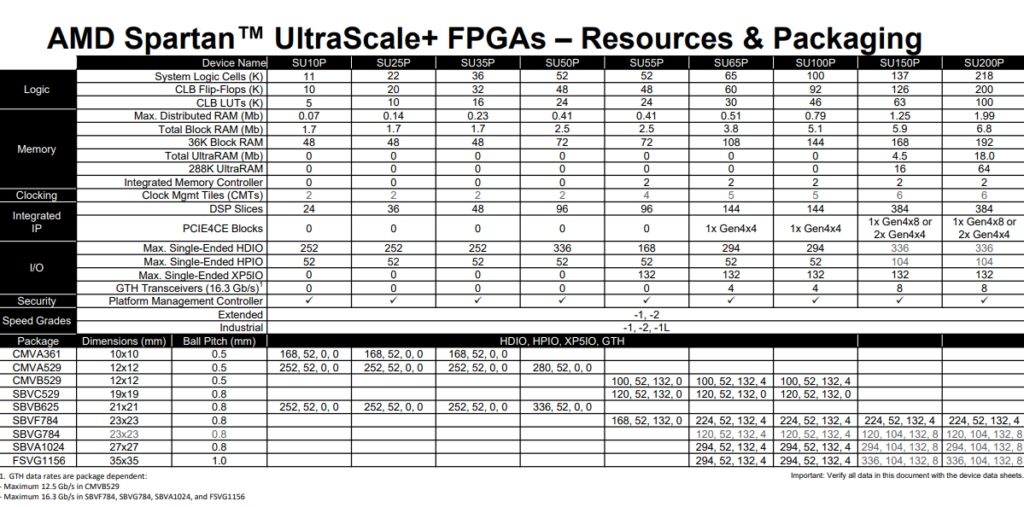

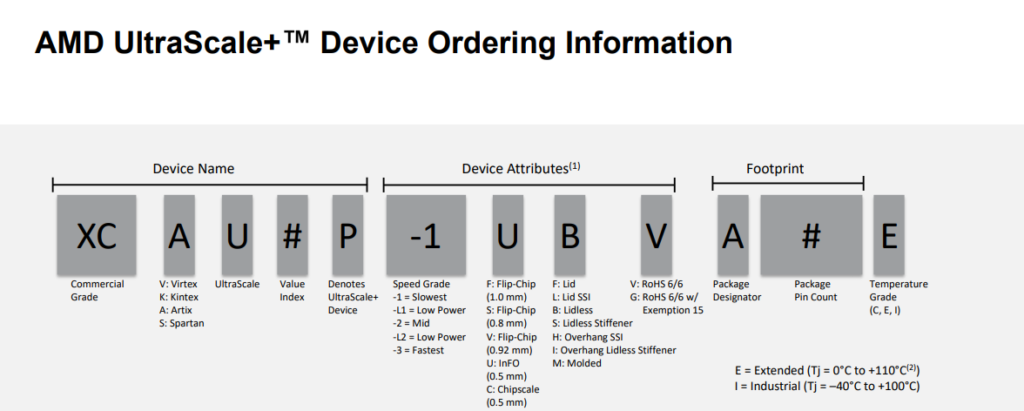

Pour en revenir avec l’annonce du jour d’AMD, il s’agit des FPGA de la gamme Spartan UltraScale+. Ceux-ci « offrent un nombre élevé d'E/S, une grande efficacité énergétique et des fonctions de sécurité de pointe pour les applications dans les secteurs de la vision embarquée, de la santé, des réseaux industriels, de la robotique et de la vidéo ».

Comme le reste des produits UltraScale+, les nouveaux FPGA sont gravés en FinFET 16 nm par TSMC. AMD revendique « le rapport E/S par cellule logique le plus élevé de l'industrie dans des FPGA construits avec une technologie 28 nm et moins ». Le comparatif chez la concurrence a été fait sur les fiches techniques publiées par Efinix, Intel, Lattice et Microchip.

Avec Spartan UltraScale+, le Texan annonce « jusqu'à 30 % d’économie d’énergie par rapport à la famille Artix 7 en 28 nm ». Atrix est également une série visant l’entrée de gamme. Au-dessus, on retrouve les séries Kintex et Virtex. Les différents modèles de puces sont disponibles dans ce document.

AMD affirme que ce sont les premiers FPGA de la gamme UltraScale+ avec un contrôleur de mémoire « LPDDR5 renforcé et une prise en charge PCle Gen4 x8 ». AMD met aussi en avant plusieurs fonctionnalités sur la sécurité. Il est question de chiffrement post quantique avec des algorithmes approuvés par le NIST ainsi que la prise en charge des clés PPK/SPK.

Il faudra toutefois être patients puisqu’AMD précise que les premiers échantillons pour évaluation des FPGA Spartan UltraScale+ « devraient être disponibles au cours du premier semestre 2025 », soit dans encore un an.

Spartan UltraScale+vient donc compléter les autres séries « UltraScale+ » (Artix, Kintex, Virtex et Zynq), toutes gravées en 16 nm FinFET par TSMC. Les gammes UltraScale (sans le +) sont en 20 nm, les séries « 7 » (Spartan 7, Artix 7…) en 28 nm et enfin la série « 6 » en 45 nm. Le cycle de vie de cette dernière s’étend jusqu’en 2030 au moins, contre 2035 minimum pour la série « 7 ».

Les annonces autour des FPGA se multiplient, AMD présente Spartan UltraScale+

-

Dis, c’est quoi un FPGA ?

-

Une « matrice de blocs de logique »

-

Altera et Xilinx : deux géants du FPGA rachetés par Intel et AMD

-

Voici les FPGA Spartan UltraScale+

Commentaires (11)

Vous devez être abonné pour pouvoir commenter.

Déjà abonné ? Se connecter

Abonnez-vousLe 05/03/2024 à 18h03

Le 05/03/2024 à 18h04

Modifié le 05/03/2024 à 20h01

De plus, vu les tailles des dies, j'aurais plutôt tendance à utiliser la méthode AMD:

foutre des technos différentes sur un package 2.5D ou 3D

Enfin, quid de la sécurité du CPU ?

Modifié le 05/03/2024 à 21h20

Chez Xilinx, dans la même famille Ultrascale+, FPGA avec quad core ARM Cortex A53, + dual core R5.

Et dans la famille des FPGA Versal, nouvelle generation chez Xilinx, on a du Cortex A72 en 7 nm.

Grosse demande sur ce genre de SoC dans l'embarqué

Le 05/03/2024 à 23h21

Le 06/03/2024 à 09h12

Mister c'est juste une application sur une carte de dev fpga.

Le 11/03/2024 à 02h28

Le 11/03/2024 à 09h43

Modifié le 06/03/2024 à 10h09

Par la suite, au lieu d'associer une armée de PAL/GAL pour avoir beaucoup de possibilités, une version avancée est apparue, les CPLD (complex PLD). Vu le nombre portes (plusieurs centaines ou milliers) et d'I/O, il n'est plus envisageable de les programmer sur un support avant soudure et on commence à voir fleurir des ports série ou JTAG pour la programmation.

Alors que la programmation par tables de vérité était suffisante pour les PAL/GAL/CPLD, des besoins de programmation avancée, pour faire des machines à état par exemple (des CPUs) et disposant de mémoire. La logique séquentielle ne suffit plus et elle est rempalcée par la logique combinatoire. Des(un) langages sont mis au point mais le principal est le VHDL (et Altera a fait sa version perso AHDL) qui sont aussi utilisés pour la conception de certains ASICs. Certains FPGA ne conservent pas leur programme à l'extinction (il faut donc les réinitialiser depuis une rom externe ou par lien série) mais les plus récents sont basés sur de la Flash.

Les derniers FPGA sont "hybrides" et vont contenir des parties telles qu'on les verrait dans un µC, ainsi il n'est pas rare de trouver un énumérateur USB, un gestionnaire de bus ou autres fonctionnalités qui simplifieront le design du fait qu'ils sont déjà embarqués dans le silicone.

Le 06/03/2024 à 13h09

Le 07/03/2024 à 09h19