AMD annonce ses « SoC adaptatifs » Versal Premium Gen 2

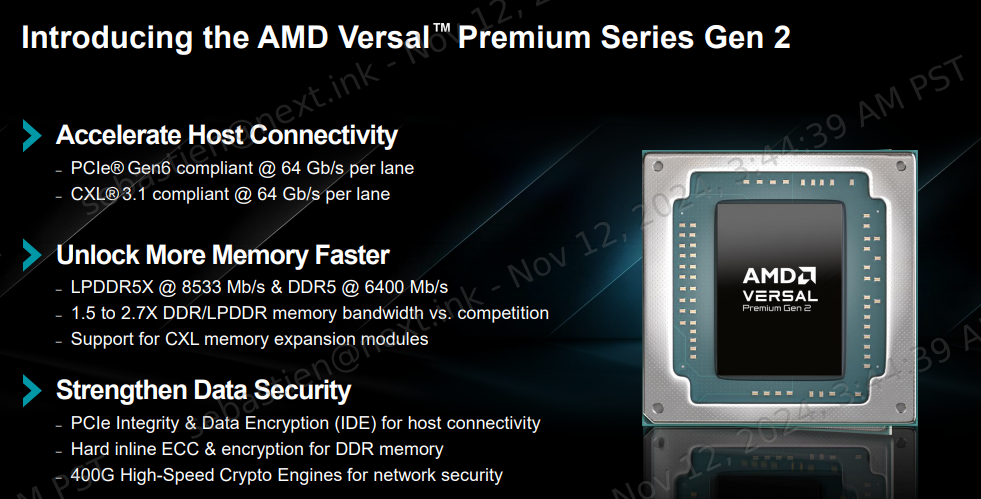

AMD annonce ses FPGA Versal Premium de seconde génération, avec le passage au PCIe 6.0, au CXL 3.1 et à la LPDDR5X. Quatre références sont annoncées, mais il faudra être patient pour la disponibilité.

Le 12 novembre à 15h12

4 min

Hardware

Hardware

Les Versal d’AMD (lancés par Xilinx, une société rachetée par AMD en 2020) sont des SoC adaptatifs (ou FPGA) « pour toutes les applications, du cloud à la périphérie ». La première génération comprend cinq gammes de produits : AI Edge, AI Core, HBM, Prime et Premium.

Les deux premières ciblent évidemment l’intelligence artificielle. AI Edge propose des « performances IA/watt exceptionnelles », tandis que la seconde cible des « performances de calcul exceptionnelles ». HBM porte bien son nom puisque cette gamme intègre de la mémoire HBM2e (High Bandwidth Memory) avec une large bande passante. AMD annonce ainsi « jusqu'à 6 fois plus de bande passante pour une consommation par bit réduite de 65 % par rapport à la série Versal Premium ».

Enfin, Prime est la « série fondamentale […] offrant une large applicabilité sur plusieurs marchés », tandis que Premium se place un cran au-dessus et vise les « applications de calcul et de mise en réseau les plus exigeantes ». AMD cite différents cas d’usage sur cette page.

Versal Premium Gen 2 : PCIe 6.0 et CXL 3.1

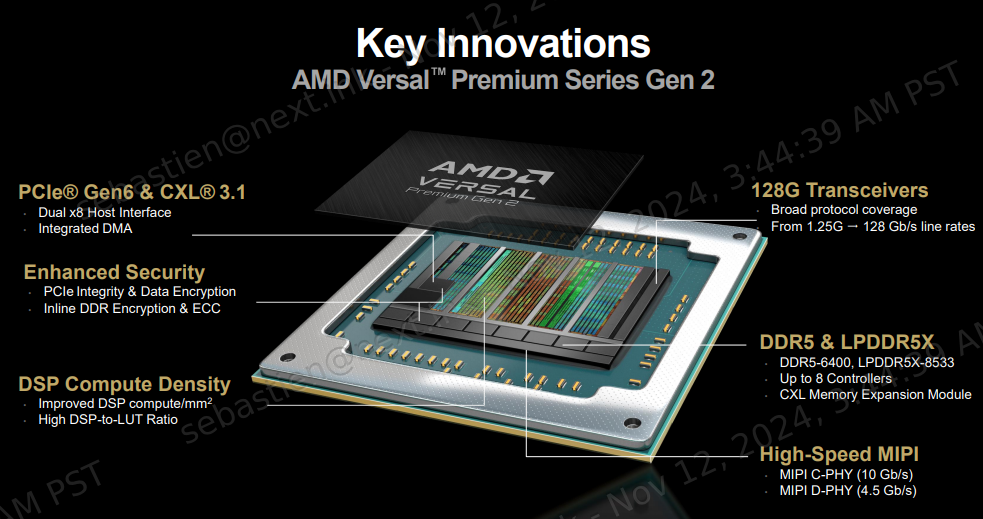

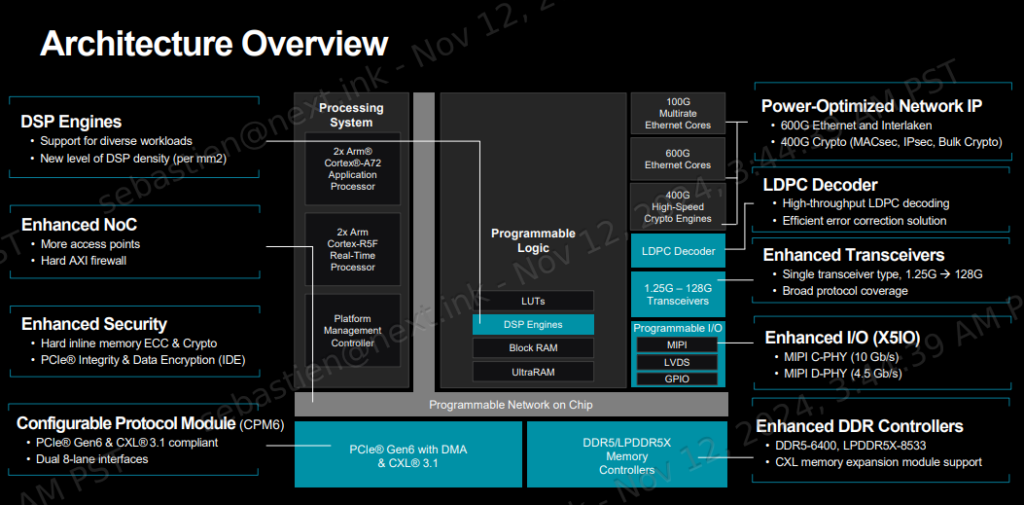

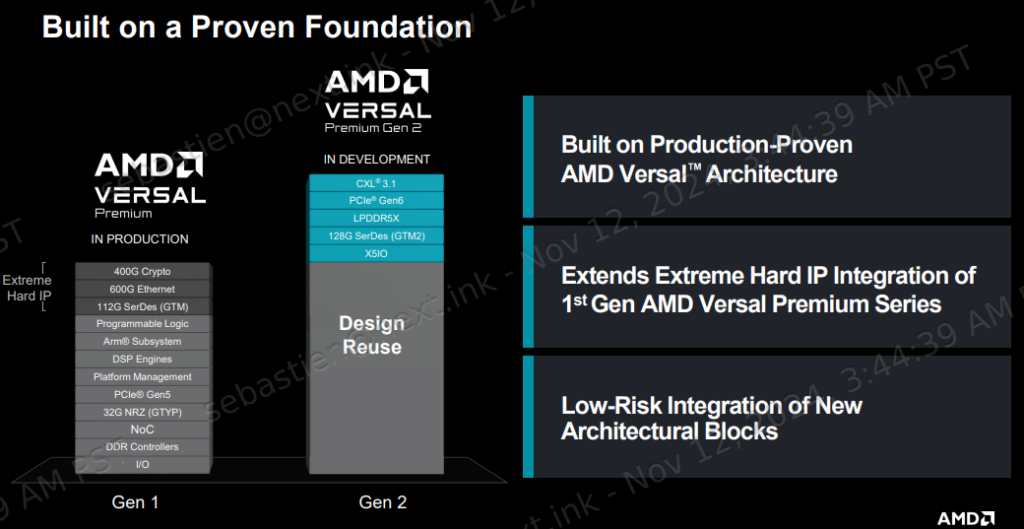

Les gammes séries AI Edge et Prime ont déjà eu droit à une seconde génération, c’est maintenant au tour de Premium de passer la seconde, avec des améliorations sur plusieurs points. Série haut de gamme oblige, on y retrouve logiquement du PCIe 6.0 avec 2 x 8 lignes, du CXL 3.1 (Compute Express Link) basé sur PCIe 6.0, ainsi que de la (LP)DDR5(X) jusqu’à 8 533 MHz avec 4 ou 8 canaux suivant les références.

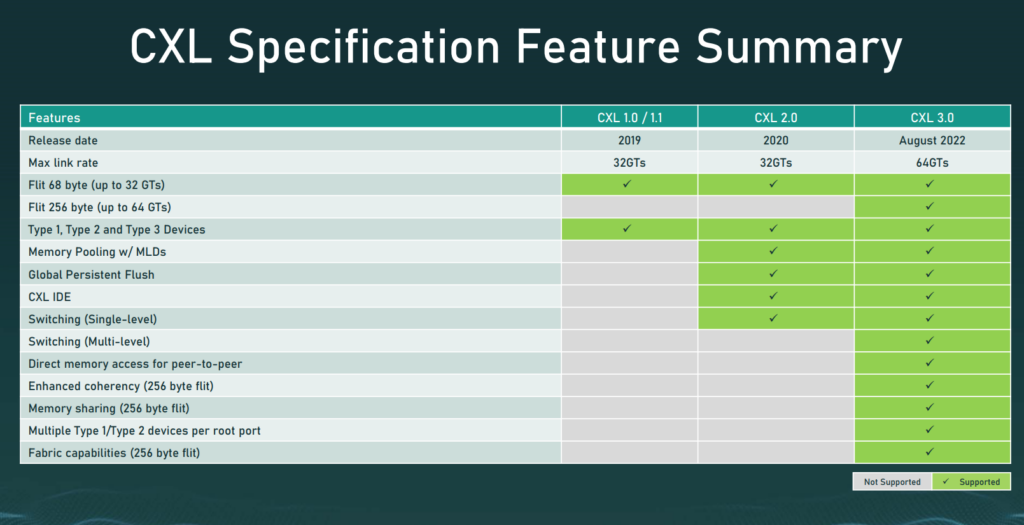

Le PCIe 6.0 propose pour rappel une bande passante de 64 GT/s (en PAM4, ou Pulse Amplitude Modulation avec 4 niveaux). Si les versions 1.x et 2.0 de CXL utilisaient la norme PCIe 5.0 (32 GT/s), CXL 3.0 et 3.1 exploitent le PCIe 6.0 avec une bande passante doublée de 64 GT/s.

Quatre références, avec 0,6 à 1,5 million de LTU

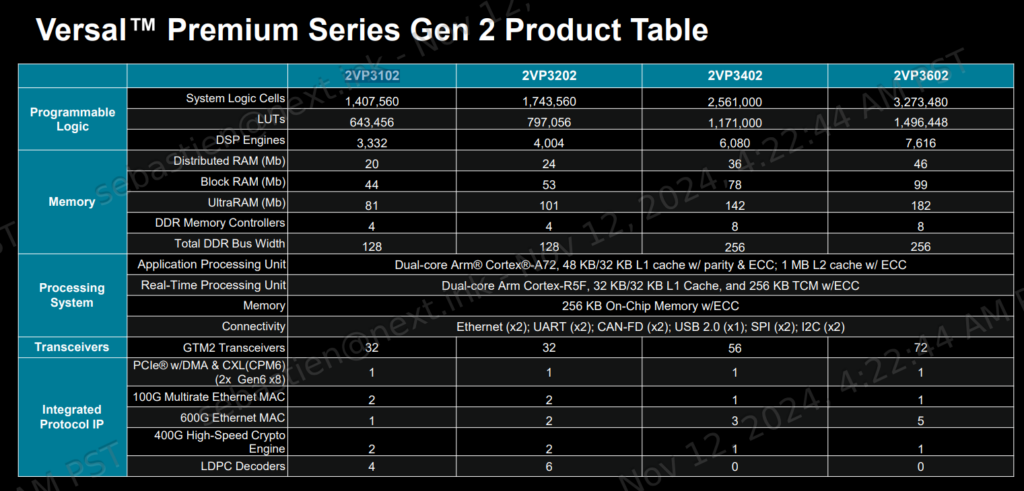

Alors que la première génération de SoC Versal Premium comprenait douze références (du VP1002 au VP1902), AMD n’en annonce que quatre nouvelles pour l’instant : les 2VP3102. 2VP3202, 2VP3402 et 2VP3602. Le 2 devant VP pour seconde génération. Le V pour Versal et P pour Premium pour rappel.

Le nouveau FPGA Versal 2VP3102 vient donc se placer en face du VP1102, avec un peu moins de cellules logiques du système (1,408 million contre 1,575 million) et donc des tables de correspondance (LookUp Table ou LUT) moins nombreuses également (643 456 contre 719 872). Par contre, le nombre de moteurs DSP est en hausse : 3 332 au lieu de 1 904.

Aucun des quatre Versal Premium Gen 2 n’a pour le moment de moteurs d'IA, comme c’est le cas des VP2502 et VP2802 (peut-être aurons-nous droit à des 2VP4x02 à l’avenir ?).

Les caractéristiques techniques complètes des nouveaux SoC adaptatifs sont regroupées sur ce tableau :

Avec « seulement » 3,273 millions de cellules logiques système, le Versal 2VP3602 est juste en dessous des Versal VP1802 et VP2802 (un VP1802 avec des moteurs d’IA) et reste très loin du record système du VP1902. Ce dernier comprend pour rappel 18,5 millions de cellules logiques et 8,46 millions de LUT, mais « seulement » 6 864 moteurs DSP, contre plus de 14 000 pour les VPx802.

Longue attente avant la disponibilité

Il faudra encore être patient, puisque la disponibilité n’est pas prévue avant le premier semestre 2026 pour les échantillons et les kits de développement. Les expéditions des puces en production devraient débuter durant la seconde moitié de 2026.

AMD annonce ses « SoC adaptatifs » Versal Premium Gen 2

-

Versal Premium Gen 2 : PCIe 6.0 et CXL 3.1

-

Quatre références, avec 0,6 à 1,5 million de LTU

-

Longue attente avant la disponibilité

Commentaires (2)

Abonnez-vous pour prendre part au débat

Déjà abonné ? Se connecter

Cet article est en accès libre, mais il est le fruit du travail d'une rédaction qui ne travaille que pour ses lecteurs, sur un média sans pub et sans tracker. Soutenez le journalisme tech de qualité en vous abonnant.

Accédez en illimité aux articles

Profitez d’un média expert et unique

Intégrez la communauté et prenez part aux débats

Partagez des articles premium à vos contacts

Abonnez-vousLe 12/11/2024 à 21h12

A la base un FPGA n'est obligatoirement utilisé pour créer un système sur puce (SOC). Pas mal de FPGA sont utilisés en compagnon d'un micro-contrôleur pour réaliser des tâches spécialisées ou des fonctions logiques pures.

Parfois, le microcontrôleur en question est placé dans le même boîtier, ce qui en fait un MCM mais pas un SOC.

Le 12/11/2024 à 21h49